I2C Master/Multi-Master/Slave

Überblick

General Description

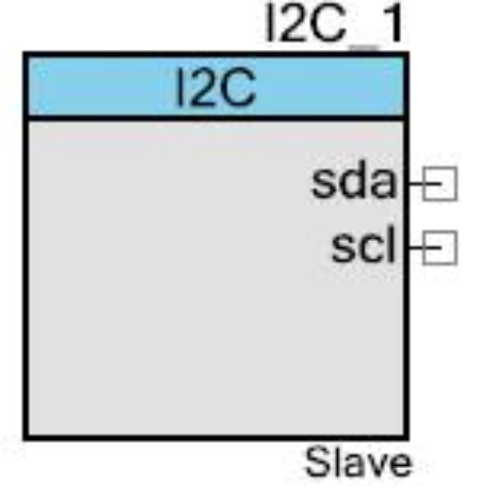

The I2C component supports I2C slave, master, and multi-master configurations. The I2C bus is an industry-standard, two-wire hardware interface developed by Philips. The master initiates all communication on the I2C bus and supplies the clock for all slave devices.

The I2C component supports standard clock speeds up to 1000 kbps. It is compatible with I2C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification. The I2C component is compatible with other third-party slave and master devices.

Note: This version of the component datasheet covers both the fixed hardware I2C block and the UDB version.

-

Industry-standard NXP I2C bus interface

-

Supports Slave, Master, Multi-Master and Multi-Master-Slave operation

-

Requires only two pins (SDA and SCL) to interface to I2C bus

-

Supports standard data rates of 100/400/1000 kbps

-

High level APIs require minimal user programming

Support