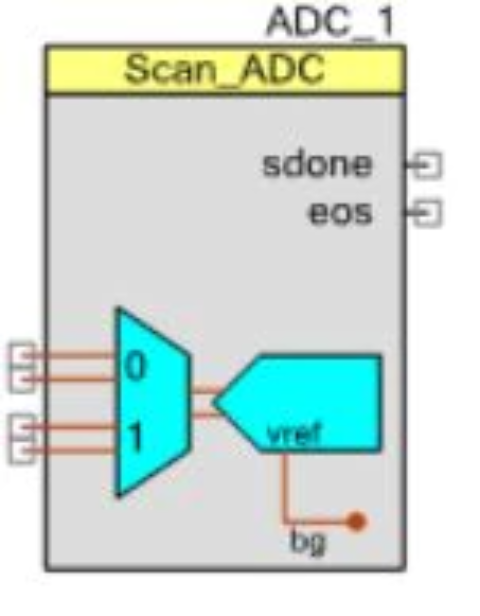

Scanning SAR ADC (Scan_ADC)

Overview

General Description

The Scanning SAR ADC Component gives configuration-, schematic-, and firmware-level support for the version of the SAR (‘Successive Approximation Register’) ADC present on the PSoC family. Up to sixteen analog channels (from sources dependent on the specific device) can be automatically scanned, either on demand or continuously, with the results placed in individual result registers. The scan scheduler adjusts internal sampling behavior and clock to accommodate specific settling time and overall scan rate requirements. Averaging can be applied to any channel in a scan.

- Available for PSoC™ 4 and PSoC™ 6

- Interleaved or channel-sequential averaging in hardware

- Up to 16-bit resolution with averaging

- Aggregate sample rate up to 1 Msps

- Single-ended and Differential input modes

- Scheduler optimizes settling time and clock to fit scan rate

- Scan up to sixteen analog signals automatically

- Four run-time selectable configurations

Support