AURIX™ Safety Software

To request a free 3-month Evaluation license or if your company already has an existing project, for TC4x SafeTlib drivers, click here.

NOTE: Users need to register in myInfineon portal to request a license (Click ‘myInfineon’ and ‘Register for myInfineon’ at top right of the Web page)

AURIX™ TC4x SafeTlib

- Set of SW tests to support top level safety requirements

- Handling of external watchdog and PMIC (Power Management IC)

Key Features:

- Coverage of AURIX™ TC4x Top Level Safety REQs (TLSRs) & External Safety Measures

- Enable safety operation of the chip (startup & runtime)

- Enablement of TLF4x PMIC

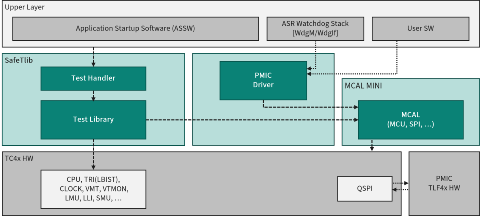

SW Architecture Overview

Key Facts / Important to Know :

- SW targeted to be ASIL-D

- ISO 26262:2018 compliance

- ISO 21434 compliance in evaluation

- ASPICE v3.1 L3 compliant development process

Feature Highlights:

- Safety test library: safety tests + watchdog handling

- Test handler: mapping tests to different cores, gather test results

- Test library:

- SMU core alive alarm test, ESM(s) supported

- Volatile memory test verifies SRAM, ECC, EDC in addition to alarm path test

- Logic build-in-self-test: configuration, trigger and result handling, alarm path test

- Voltage Monitoring: test config, result handling, ESM(s) supported

- Temperature Monitoring: Die temperature test

- Bus, Clock, NVM, WTU, XSPI monitor: Alarm path test

- WatchDog handling

- Ready-to-use handling of external watch dog

- Enablement and driver of TLF4x PMIC Scalable & flexible power supply solution for TC4x

AURIX™ TC3xx Safety Software SBST Deliverables

SBST for non LS CPU – Supporting ASIL-B

- The CPU Software Based Self Test (SBST) is a safety mechanism that supports the ISO26262 SPFM for ASIL B safety goals. The SBST detects Permanent Random Hardware Faults in the fetch unit and pipelines of non-lockstep CPU cores with a diagnostic coverage level of 90%.

- Required for applicants with an ASIL B requirement on AURIX™ TC3xx non-lockstep CPUs.

SBST for SPU – Supporting ADAS Cluster ASIL-C Applications

- The SPU Software Based Self Test (SBST) is a safety mechanism that supports the ISO26262 SPFM and is similar in concept to the CPU SBST described above.

AURIX™ TC2xx SafeTlib

- Set of SW tests to support applications with functional safety requirements including “Software-Based Self Test” (SBST) for the CPU core

- Support of system integration with application-dependent tests

- Handling of internal and external watchdogs (SafeWDG)