Pulse Width Modulator (TCPWM_PWM_PDL)

General Description

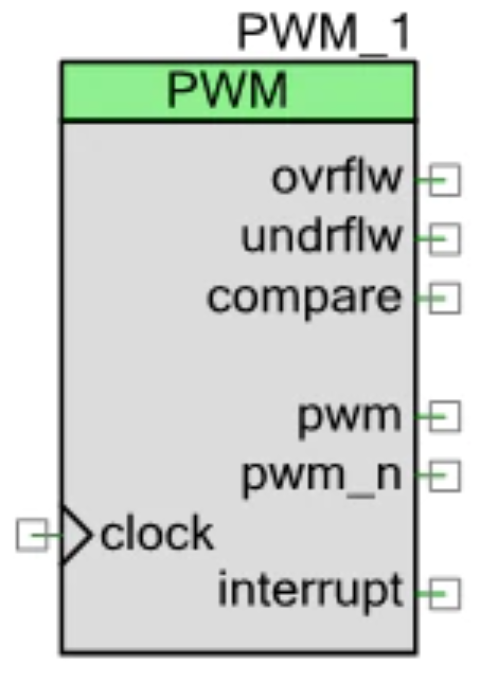

The TCPWM_PWM_PDL Component is a graphical configuration entity built on top of the cy_tcpwm driver available in the PDL. It allows schematic-based connections and hardware configuration as defined by the Component Configure dialog.

The TCPWM_PWM_PDL Component is a wrapper around the TCPWM hardware that allows you to configure the TCPWM hardware for PWM Functionality. It allows for the creation of arbitrary digital waveforms. You can control the duty cycle and period of the TCPWM_PWM_PDL output signal. The TCPWM_PWM_PDL also provides a complementary output, with the possibility to insert dead time between the two outputs.

The TCPWM_PWM_PDL Component has several alignment options: Left, Right, Center, and Asymmetric. In all modes the period and compare value can be swapped to create an arbitrary waveform. It also has a pseudo random output mode.

- 16 or 32 bit Counter

- Two Programmable Period Registers, that can be swapped

- Two Output Compare registers than can be swapped on overflow and/or underflow

- Left Aligned, Right Aligned, Center Aligned, and Asymmetric Aligned Modes

- Continuous or One Shot Run Modes

- Pseudo Random Mode

- Two PWM outputs with Dead Time insertion, and programmable polarity

- Interrupt and Output on Overflow, Underflow, or Compare

- Start, Reload, Kill, Swap, and Count Inputs

- Multiple Components can be synchronized together for applications such as three phase motor control

- Peripheral Driver Library (PDL) Component (PDL Application Programming Interface (API) only)