# **PSOC<sup>™</sup> 4 MCU hardware design considerations**

### About this document

#### Scope and purpose

This application note shows you how to design a hardware system around a PSOC<sup>™</sup> 4 MCU device, starting with considerations for package selection, power, clocking, reset, I/O usage, programming and debugging interfaces, and analog module design.

#### **Intended audience**

This document is primarily intended for engineers who need to become familiar with the hardware design principles of PSOC<sup>™</sup> 4 MCU devices.

### Table of contents

## **Table of contents**

| Abou   | t this document                          | . 1 |

|--------|------------------------------------------|-----|

| Table  | e of contents                            | . 2 |

| 1      | Introduction                             | . 3 |

| 2      | Package selection                        | . 4 |

| 3      | Power                                    | . 5 |

| 3.1    | Power pin connections                    | 5   |

| 3.1.1  | Unregulated external supply mode         | 5   |

| 3.1.2  | Regulated external supply mode           | 6   |

| 3.1.3  | Other power supply considerations        | 7   |

| 3.2    | Power ramp-up (slew rate) considerations | 7   |

| 3.3    | Device power settings                    | 7   |

| 3.4    | Thermal considerations                   | 9   |

| 4      | Clocking                                 | 10  |

| 4.1    | Clocking settings                        | 10  |

| 5      | Reset                                    | 12  |

| 6      | Programming and debugging                | 13  |

| 7      | GPIO pins                                | 15  |

| 7.1    | I/O pin selection                        | 15  |

| 7.2    | Special ports                            | 16  |

| 8      | Component placement                      | 19  |

| 9      | Analog module design tips                | 21  |

| 9.1    | SAR ADC                                  | 21  |

| 9.1.1  | SAR ADC acquisition time                 | 23  |

| 9.2    | Opamps                                   | 26  |

| 9.3    | Comparators                              | 27  |

| 9.4    | CAPSENSE™                                | 28  |

| 9.5    | Current DACs (IDACs)                     | 29  |

| 10     | Summary                                  | 31  |

| 11     | Appendix A - Schematic checklist         | 32  |

| 12     | Appendix B - PCB layout tips             | 34  |

| Refer  | rences                                   | 36  |

| Revis  | sion history                             | 38  |

| Discla | aimer                                    | 40  |

|        |                                          |     |

### Introduction

## 1 Introduction

PSOC<sup>™</sup> 4 is a powerful, programmable microcontroller with an Arm<sup>®</sup> Cortex<sup>®</sup>-M0 or Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ CPU. It provides the capability and flexibility for analog and digital applications beyond what traditional MCUs offer. Currently, the PSOC<sup>™</sup> 4 MCU portfolio contains the following families:

- PSOC<sup>™</sup> 4000 family: PSOC<sup>™</sup> 4000, PSOC<sup>™</sup> 4000S, PSOC<sup>™</sup> 4000T

- PSOC<sup>™</sup> 4100 family: PSOC<sup>™</sup> 4100, PSOC<sup>™</sup> 4100S, PSOC<sup>™</sup> 4100S Plus, PSOC<sup>™</sup> 4100S Plus 256K, PSOC<sup>™</sup> 4100PS, PSOC<sup>™</sup> 4100M, PSOC<sup>™</sup> 4100L, PSOC<sup>™</sup> 4100S Max, PSOC<sup>™</sup> 4100BL

- PSOC<sup>™</sup> 4200 family: PSOC<sup>™</sup> 4200, PSOC<sup>™</sup> 4200M, PSOC<sup>™</sup> 4200L, PSOC<sup>™</sup> 4200DS, PSOC<sup>™</sup> 4200BL

- PSOC<sup>™</sup> 4500 and PSOC<sup>™</sup> 4700 family: PSOC<sup>™</sup> 4500S, PSOC<sup>™</sup> 4700S

- PSOC<sup>™</sup> 4 AIROC<sup>™</sup> Bluetooth<sup>®</sup> LE

This application note discusses considerations for hardware design including package, power, clocking, reset, I/O use, programming, and debugging; and provides design tips for analog modules for these device families. It also discusses good board-layout techniques, which are particularly important for precision analog applications.

The PSOC<sup>™</sup> 4 MCU device must be configured to work in its hardware environment, which you can do with integrated design environments (IDE) like PSOC<sup>™</sup> Creator or ModusToolbox<sup>™</sup> IDE; see the "PSOC<sup>™</sup> 4 feature set" section of AN79953 – Getting started with PSOC<sup>™</sup> 4 [1] to know which IDE is supported for each PSOC<sup>™</sup> 4 device. The application note explains various configurations available in PSOC<sup>™</sup> Creator and ModusToolbox<sup>™</sup> IDE required to set up the device for a given hardware environment.

This application note assumes that you have some basic familiarity with PSOC<sup>™</sup> 4 MCU devices, PSOC<sup>™</sup> Creator, and ModusTooolbox<sup>™</sup> software. If you are new to ModusToolbox<sup>™</sup> IDE, see the ModusToolbox<sup>™</sup> software user guide, which provides a high-level overview of the ModusToolbox<sup>™</sup> software. To get started with PSOC<sup>™</sup> 4 MCU, see AN79953 – Getting started with PSOC<sup>™</sup> 4 [1]. PSOC<sup>™</sup> 4 Bluetooth<sup>®</sup> LE related topics are covered in AN91267 - Getting started with PSOC<sup>™</sup> 4 CY8C4xxx-BL MCU with AIROC<sup>™</sup> Bluetooth<sup>®</sup> LE [16]. The PSOC<sup>™</sup> 4 AIROC<sup>™</sup> Bluetooth<sup>®</sup> LE family has an important topic for hardware design – Bluetooth<sup>®</sup> LE antenna design. As it involves specific RF expertise, this topic is explored in other application notes. See References [7] for more information.

### Package selection

## 2 Package selection

One of the first decisions you must make for your PCB is the choice of package. Several considerations drive this decision, including the number of PSOC<sup>™</sup> MCU device pins required, PCB and product size, PCB design rules, and thermal and mechanical stability. PSOC<sup>™</sup> MCU devices are available in the following packages with different characteristics.

- **Small-outline integrated circuit (SOIC):** This package type is evolved from dual in-line package (DIP). It has two lines of pins and is generally used for chips with a small number of pins (less than 20). Because it has a very large pitch, it is easy to route signals and manually solder. It also provides a good mechanical stability.

- **Thin quad flat package (TQFP):** This package type makes it easy to route signals due to the large pitch and the open area below the part. Disadvantages are a larger package size and lower mechanical stability.

- **Shrink small-outline package (SSOP):** This package type provides the same advantages and disadvantages as the TQFP package.

- **Quad flat no-lead (QFN):** This package type is much smaller than the other packages. The central exposure pad gives the package the best heat dispersion performance and mechanical stability. Disadvantages are that it is more difficult to route signals due to the center pad. For more information, see AN72845 Design guidelines for Infineon quad flat no-lead (QFN) packaged devices [2].

- Wafer level chip-scale package (WLCSP): This package type makes the chip size as small as the die. All pins are led as balls underneath the package. The extremely tiny size of the package makes it a perfect option for the scenarios where the PCB room is critical, such as in portable applications. The disadvantage is that the package provides less mechanical stability than other packages.

- Very fine-pitch ball grid array (VFBGA): This package type is used for devices with large number of I/Os, as it provides a miniature package for more than hundreds of pins. The disadvantage is a low mechanical stability.

As a design reference, see PSOC<sup>™</sup> 4 CAD libraries, which contain PSOC<sup>™</sup> 4 MCU schematics and PCB libraries. Note that you may need to modify the libraries slightly when you use them in your hardware design. Infineon takes no responsibility for issues related to the use of the libraries.

## 3 Power

PSOC<sup>™</sup> 4 MCU can be powered by a single supply with a wide voltage range, from 1.71 V to 5.5 V. As listed in Table 1, it has separate power domains for analog and digital modules. V<sub>DDA</sub> is the analog power supply pin, VSSA is the analog ground pin, V<sub>DDD</sub> and V<sub>CCD</sub> are the digital power supply pins, V<sub>DDIO</sub> is the power supply pin for I/Os, V<sub>SS</sub> is the digital ground pin, and V<sub>DDR</sub> is the RF power pin.

| Table 1PSOC <sup>™</sup> 4 MCU power domains |

|----------------------------------------------|

|----------------------------------------------|

| Power domain | Associated pins                  |  |

|--------------|----------------------------------|--|

| Analog       | $V_{DDA}, V_{SSA}$               |  |

| Digital      | $V_{ddd}$ , $V_{ccd}$ , $V_{ss}$ |  |

| I/O          | V <sub>DDIO</sub>                |  |

| RF           | V <sub>DDR</sub>                 |  |

Note: V<sub>DDIO</sub> is available only in certain device families/packages. I/Os are powered from V<sub>DDD</sub> in devices without a V<sub>DDIO</sub> pin. In some packages, V<sub>DDA</sub> and V<sub>DDD</sub> are combined into a single V<sub>DDD</sub> pin, and V<sub>SSA</sub> and V<sub>SS</sub> are combined into a single V<sub>SS</sub> pin. V<sub>DDR</sub> is available only in PSOC<sup>™</sup> 4 AIROC<sup>™</sup> Bluetooth<sup>®</sup> LE family devices. The V<sub>DDR</sub> supply should always be lesser than equal to the applied V<sub>DDD</sub> supply.

## 3.1 Power pin connections

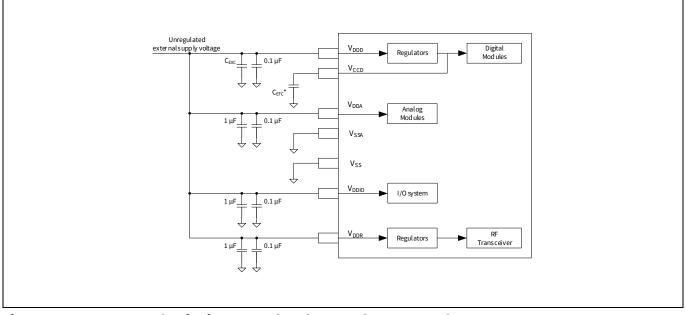

PSOC<sup>™</sup> 4 MCU devices can be powered by two modes of power supply: Unregulated external supply and regulated external supply modes. Power pin connections for these two modes are illustrated in Figure 1 and Figure 2.

## 3.1.1 Unregulated external supply mode

Refer to the device datasheet for the recommended unregulated external supply voltage (V<sub>DD</sub>) range.

In this mode, internal regulators convert the  $V_{DDD}$  input into the supply voltage for the device digital domain. Output voltage from these internal regulators are also routed to the  $V_{CCD}$  pin. In such cases, do not power this pin or connect any external load to  $V_{CCD}$ , except a decoupling capacitor,  $C_{EFC}$ , indicated in the corresponding device family datasheet and in Figure 1.

Also, in this mode, some other internal regulators convert the V<sub>DDR</sub> input into the power supply for the Bluetooth<sup>®</sup> LE RF transceiver. Note that the regulators for the RF transceiver in a Bluetooth<sup>®</sup> LE device stop working when V<sub>DDR</sub> is lower than 1.9 V.

Figure 1An example of using unregulated external power supply

Note: For the Bluetooth<sup>®</sup> LE family, this capacitor is denoted by  $C_{VCCD}$  in the datasheet.

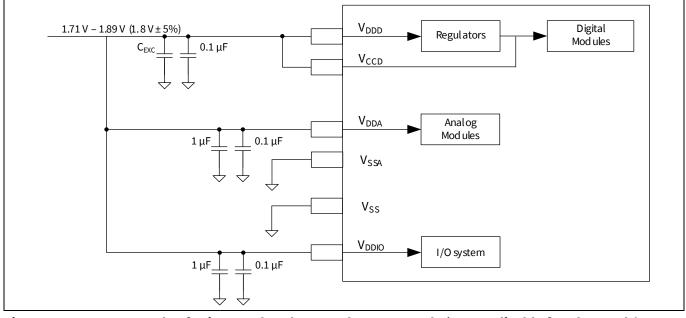

## 3.1.2 Regulated external supply mode

You can also power PSOC<sup>™</sup> 4 MCU (except the Bluetooth<sup>®</sup> LE family) with a regulated 1.8-V (±5%) external supply, as Figure 2 shows. The V<sub>CCD</sub> pins must be tied to the VDDD pin and powered directly with this externally regulated supply. The unused regulators within PSOC<sup>™</sup> can be disabled by setting the EXT\_VCCD bit in the PWR\_CONTROL register to reduce power consumption. For more information, see the PSOC<sup>™</sup> 4 MCU device datasheets and reference manuals.

# Figure 2 An example of using regulated external power supply (not applicable for Bluetooth<sup>®</sup> LE family)

## 3.1.3 Other power supply considerations

In both modes, connect one  $0.1-\mu$ F and one ceramic decoupling capacitor,  $C_{EXC}$ , mentioned in the device datasheet to each power supply pin (note that certain packages have more than one  $V_{DDD}$ ,  $V_{DDA}$ , and  $V_{DDIO}$  pin). The PCB trace between the pin and the capacitors should be as short as possible. For more information, see Appendix B - PCB layout tips.

Note: It is a good practice to check a capacitor's datasheet before you use it, specifically for working voltage and DC bias specifications. With some capacitors, the actual capacitance can decrease considerably when the DC bias is a significant percentage of the rated working voltage.

You can use a single power supply rail for digital power and analog power, which helps to simplify the power design in your board. However, to get a better analog performance in a mixed-signal circuit design, use separate power supply rails for the digital power and the analog power. In all cases, ensure that VDDIO ≤ VDDD ≤ VDDA. For more mixed-signal circuit design techniques, see AN57821 - PSOC<sup>™</sup> 3, PSOC<sup>™</sup> 4, and PSOC<sup>™</sup> 5LP mixed-signal circuit board layout considerations [5].

Proper use and layout of capacitors and ferrite beads help to improve the EMC performance.

The PSOC<sup>™</sup> 4 MCU kit webpages (CY8CKIT-040, CY8CKIT-040T, CY8CPROTO-040T, CY8CPROTO-040T-MS, CY8CKIT-041-41XX, CY8CKIT-042, CY8CKIT-042-BLE, CY8CKIT-043, CY8CKIT-044, CY8CKIT-045S, CY8CKIT-046, CY8CKIT-145, CY8CKIT-147, CY8CKIT-149, CY8CKIT-041S-Max, CY8CKIT-148, and CY8CKIT-148-COIL) provide schematics and bills of material (BOMs) that give good examples of how to incorporate PSOC<sup>™</sup> 4 into board schematics. For more information, see References.

## 3.2 Power ramp-up (slew rate) considerations

As mentioned previously in Section Power pin connections, if you use separate power rails for analog and digital power domains, the voltage at the V<sub>DDA</sub> pin must always be greater than or equal to the voltage at the V<sub>DDD</sub> pin. When PSOC<sup>™</sup> 4 MCU is powered up, the voltage at the V<sub>DDA</sub> pin must be present before or at the same time as the voltage at the V<sub>DDD</sub> pin. The maximum allowed voltage ramp rate for any power pin is 67 mV/µs.

## 3.3 Device power settings

Use PSOC<sup>™</sup> Creator or Eclipse IDE for ModusToolbox<sup>™</sup> software to configure the device power settings<sup>1</sup>. Both the tools use this information to configure the device for optimal performance. If you are using PSOC<sup>™</sup> Creator, to open the Design-Wide Resources (DWR) window, double-click the *.cydwr* file in the project navigator and navigate to the **System** tab to configure the settings as shown in Figure 3.

<sup>&</sup>lt;sup>1</sup> See AN79953 - Getting started with PSOC<sup>™</sup> 4 MCU [1] to know which IDE is supported for each PSOC<sup>™</sup> 4 MCU device. Application note 7

## **PSOC<sup>™</sup> 4 MCU hardware design considerations**

#### Power

| Eile       Edit       View       Project       Build       Debug         Image: Im                                                                                                       | <u>I</u> ools <u>W</u> indow <u>H</u> elp<br>♥ , 49% • ♥ ♥ ♥ <b>A</b> • , Debug • , ∰ • ≧ 參 | 喧 👺 🍝 🖕                       |                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------|----------------|

| Workspace Explorer (1 project) 🚽 🕈 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Start Page TopDesign.cysch PSoC_4ct.cydwr                                                   | - 4 ▷ >                       | × 🛐            |

| 9. Ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | S Reset Expand E Collapse                                                                   |                               |                |

| Workspace 'PSoC_4_Project' (1 Projects)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Option                                                                                      | Value                         |                |

| Project 'PSoC_4_Project' [CY8C424 of Comparison of CY8C424 of Cy8C424 of Comparison of Cy8C424 of C | Configuration                                                                               |                               | Resource Meter |

| PSoC 4 Project.cydwr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Programming\Debugging                                                                       |                               | - eter         |

| 🖻 🧀 Header Files 🥂 🥂                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Operating Conditions                                                                        |                               |                |

| 🖻 🗁 Source Files 🔤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Variable VDDA                                                                               |                               |                |

| main.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             | 5                             |                |

| and the second sec                                                                                                                                                                                                                                             |                                                                                             | 5                             |                |

| D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             | 5                             |                |

| Datasheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                             |                               |                |

| zieer<br>zie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ····· VBUS (V)                                                                              | 5.0                           |                |

| $\prec$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                               |                |

| Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                               |                |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |                               |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Option to assign a clock for low voltage analog pump.                                       |                               |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | opion to assign a clock to now voltage analog pump.                                         |                               |                |

| ↓<br>▼ 4 III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 🔗 Pins M. Analog 📴 DMA 🕑 Clocks 💉 Interrupts                                                | 👂 System 🛛 🖺 Directives 🖉 🖬 🕨 | -              |

| Output Notice List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |                               |                |

Figure 3 Device power settings in PSOC<sup>™</sup> Creator

In Eclipse IDE for ModusToolbox<sup>™</sup> software, open the device configurator to view the **System** tab and select **Power** to configure the device power settings, as Figure 4 shows.

| CY8C4149AZI-S598                   |                         |          |                  | Ро | wer - Parameters                |                            |          |   |   | 0 X |

|------------------------------------|-------------------------|----------|------------------|----|---------------------------------|----------------------------|----------|---|---|-----|

| Peripherals Pins                   | Analog-Routing System   | Perip    | heral-Clocks DMA | En | ater filter text                |                            | <i>R</i> | Ű | E | Ŧ   |

| Enter filter text                  | a 🝸 🖻 🖽                 | K        | D D 🔍 🔍 💥        |    | me<br>Documentation             | Value                      |          |   |   |     |

| Resource                           | Name(s)                 | Pers *   |                  |    | SysPm API Reference             | Open SysPm Documentation   |          |   |   |     |

| ✓ Debug                            | cpuss_0_dap_0           | De       |                  | Ŧ  | RTOS                            |                            |          |   |   |     |

| ✓ Power                            | srss_0_power_0          | Por      |                  |    | System Idle Power Mode          | System Deep Sleep          |          |   |   | -   |

| 🝷 🍘 System Clocks                  | srss_0_clock_0          | Sys      |                  |    | ② Deep Sleep Latency (ms)       | 0                          |          |   |   |     |

| <ul> <li>High Frequency</li> </ul> |                         | <u> </u> |                  | •  | Operating Conditions            |                            |          |   |   |     |

| HFCLK                              | srss_0_clock_0_hfclk_0  | HF       |                  |    | VDDA Voltage (mV)               | 5000                       |          |   |   |     |

| SYSCLK                             | srss_0_clock_0_sysclk_0 | SY:      |                  |    | VDDD Voltage (mV)               | 5000                       |          |   |   |     |

| ▼ Input                            |                         |          |                  |    |                                 | arameters to configure the |          |   |   |     |

| ECO                                | exco_0                  |          |                  |    | ` <b></b> _`                    | power supply and mode      |          |   |   |     |

| EXTCLK                             | srss_0_clock_0_ext_0    |          |                  |    |                                 | settings                   |          |   |   |     |

| ILO                                | srss_0_clock_0_ilo_0    |          |                  |    |                                 |                            |          |   |   |     |

| 😰 ІМО                              | srss_0_clock_0_imo_0    | IM       |                  |    |                                 |                            |          |   |   |     |

| WCO                                | wco_0                   |          |                  |    |                                 |                            |          |   |   |     |

| <ul> <li>Miscellaneous</li> </ul>  |                         |          |                  | L  |                                 |                            |          |   |   |     |

|                                    | cree 0 clock 0 lfelk 0  |          |                  | P  | Power - Parameters Code Preview | v                          |          |   |   |     |

Figure 4

Device power settings in device configurator on ModusToolbox™ software

The **Variable VDDA** feature helps the PSOC<sup>™</sup> MCU device internal analog routing switch operations by charging pumps when the PSOC<sup>™</sup> MCU device analog power supply is low. It is enabled by default when the configured VDDA is lower than or equal to 4.0 V. You can disable it to save power when VDDA exceeds 4.0 V. See the PSOC<sup>™</sup> Creator system reference guide for more information.

## 3.4 Thermal considerations

Thermal considerations are important in the hardware design processes such as package selection and PCB layout. PSOC<sup>™</sup> 4 MCU targets low-power applications, as it consumes no more than 0.2 W. The maximum power consumption is so low that thermal considerations are unnecessary.

### Clocking

## 4 Clocking

PSOC<sup>™</sup> 4000 / PSOC<sup>™</sup> 4000S and PSOC<sup>™</sup> 4100 / PSOC<sup>™</sup> 4200 / PSOC<sup>™</sup> 4100S / PSOC<sup>™</sup> 4100PS / PSOC<sup>™</sup> 4500S / PSOC<sup>™</sup> 4100S Max / PSOC<sup>™</sup> 4000T have two oscillators: an internal main oscillator (IMO), which drives the high-frequency clock (HFCLK), and an internal low-speed oscillator (ILO), which drives the low-frequency clock (LFCLK). No external crystal is required for IMO and ILO. The IMO is rated at ±2 percent accuracy.

Other than the IMO and ILO, PSOC<sup>™</sup> 4100M / PSOC<sup>™</sup> 4200M / PSOC<sup>™</sup> 4100L / PSOC<sup>™</sup> 4200L / PSOC<sup>™</sup> 4000S / PSOC<sup>™</sup> 4100PS / PSOC<sup>™</sup> 4100S Max provides an additional watch crystal oscillator (WCO), which provides ±50 ppm accuracy. You can hook a 32.768-kHz crystal up to the fixed pins to get an alternative, high-accuracy clock for the LFCLK. Note that the WCO of PSOC<sup>™</sup> 4000S / PSOC<sup>™</sup> 4100S / PSOC<sup>™</sup> 4100PS /

Other than IMO, ILO, and WCO, PSOC<sup>™</sup> 4100BLE / PSOC<sup>™</sup> 4200BLE / PSOC<sup>™</sup> 4100L / PSOC<sup>™</sup> 4200L / PSOC<sup>™</sup> 4100S Max provides an additional external crystal oscillator (ECO), which provides ±50 ppm accuracy. You can hook a 24-MHz crystal up to the fixed pins to get an alternative, high-accuracy clock for the HFCLK.

A way to get high-accuracy clock for all PSOC<sup>™</sup> 4 MCU devices is to bring in a precision clock via the EXT\_CLK pin to drive the HFCLK. The external clock's frequency can be up to 48 MHz. Its duty cycle must be from 45 percent to 55 percent; a square-wave clock is recommended. Check datasheets to get where the EXT\_CLK pin is located on different PSOC<sup>™</sup> 4 MCU devices.

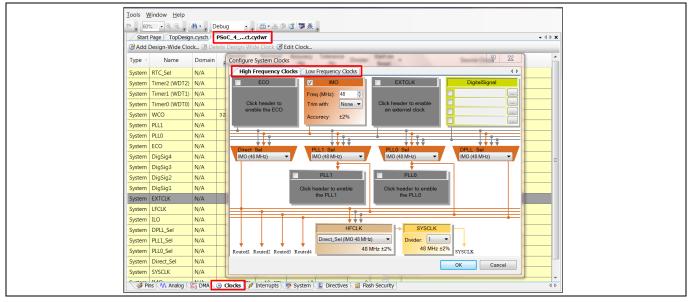

## 4.1 Clocking settings

You can use PSOC<sup>™</sup> Creator or ModusToolbox<sup>™</sup> software to manage clocks<sup>2</sup>.

If you are using PSOC<sup>™</sup> Creator, you can configure sources and paths for HFCLK and LFCLK that are configurable in two independent sub-tabs (**High Frequency Clocks** and **Low Frequency Clocks**). Switch to **Clocks** tab in the DWR window, and double-click any row in the table of clocks to open the **Configure System Clocks** dialog, as Figure 5 shows.

<sup>&</sup>lt;sup>2</sup> See "PSOC<sup>™</sup> 4 feature set" section of the AN79953 - Getting started with PSOC<sup>™</sup> 4 MCU application note to know which IDE is supported for each PSOC<sup>™</sup> 4 MCU device.

### Clocking

PSOC<sup>™</sup> 4 MCU provides flexible internal clock routing solutions. You can use up to four digital signals in PSOC<sup>™</sup> 4 MCU as the routed clock for internal digital logic, which are generally implemented with UDB resources. Select **Topics** in the PSOC<sup>™</sup> Creator Help menu and search "Configure System Clocks" to get more information.

In Eclipse IDE for ModusToolbox<sup>™</sup> software, the System tab in the device configurator (design.modus) provides the options to configure the clocks. Figure 6 shows how to configure system clocks using ModusToolbox<sup>™</sup> software.

| CY8C4149AZI-S     | 598    |                       |          |                   |                      |             | IN | 10 - Parameters   |                                 |                   |        | ð x     |

|-------------------|--------|-----------------------|----------|-------------------|----------------------|-------------|----|-------------------|---------------------------------|-------------------|--------|---------|

| Peripherals       | Pins   | Analog-Routing        | System   | Peripheral-Clocks | DMA                  |             | Er | nter filter text  |                                 |                   | U   E  | ∃ ⊞     |

| Enter filter text |        |                       |          | a 🗸 🔻             | ▣                    | X 🗈 🗅 🔍 S 🔀 | N  | ame               | Val                             | ue                |        |         |

| Resource          |        | Name(s)               |          |                   |                      |             | ~  | Peripheral Docume | ntation                         |                   |        |         |

| ✓ Debug           |        | cpuss_0_dap_0         |          |                   |                      |             |    | ? Configuration   | on Help <u>Op</u>               | <u>en IMO D</u>   | ocumer | ntation |

| EM_EEPR           |        | srss_0_eeprom_0       |          |                   |                      |             | ~  | Internal          |                                 |                   |        |         |

| ✓ Power           | Olwi   | srss_0_power_0        |          |                   |                      |             |    | Frequency (       | (MHz) 48                        |                   |        | ~       |

|                   | Clasks | srss_0_clock_0        | IMO      |                   |                      | PUMPCLK     | ~  | General           |                                 |                   |        |         |

| 🖌 🖌 System (      | LIOCKS | STSS_U_CIOCK_U        | 48 MHz ± |                   |                      | HFCLK       | L  | Frequency         | <u>a</u>                        | 48 MHz            | ± 2%   |         |

|                   | _ ► C  | lock Source selection |          |                   | Autocholog Timer (WD |             |    | , Pi              | arameters to con<br>Clock Souri | figure the<br>les |        |         |

| <                 |        |                       | >        |                   |                      |             |    | MO - Parameters   | Code Previe                     | ew                |        |         |

Figure 6 Clock settings in device configurator on ModusToolbox<sup>™</sup> software

Note: Unlike PSOC<sup>™</sup> 3 and PSOC<sup>™</sup> 5LP MCU devices, PSOC<sup>™</sup> 4 MCU cannot route the high-frequency clock (HFCLK) directly to any pin owing to its unique internal clock path structure.

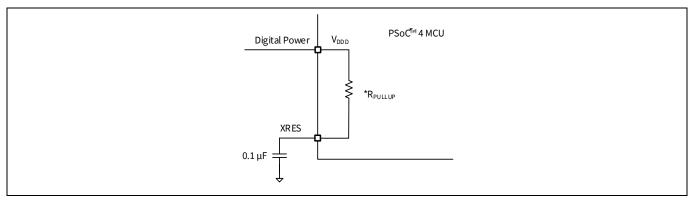

## 5 Reset

The PSOC<sup>TM</sup> 4 MCU has a reset pin, XRES, which is active LOW. XRES is internally pulled up to  $V_{DDD}$  via a resistor called \* $R_{PULLUP}$ . The value of \* $R_{PULLUP}$  is specified in the XRES section of the "Electrical Specification" chapter of the device datasheet. If this resistor value is very high, you may need to add an external resistor to XRES for reducing the system startup time.

You can connect a capacitor to the XRES pin, as Figure 7 shows, to filter out glitches, i.e., any pulses below 50 ns will filter out, thus giving the reset signal better noise immunity. The reset signal requires a pulse-width of at least 5  $\mu$ s. Typically, a capacitance of 0.1  $\mu$ F is used in the pin.

Figure 7XRES pin connection

**Programming and debugging**

## 6 Programming and debugging

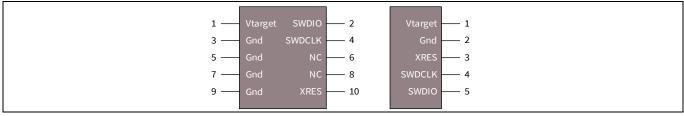

PSOC<sup>™</sup> 4 MCU supports serial wire debug (SWD) interfaces for device programming and debugging. For programming or debugging, you can use the built-in debugger of PSOC<sup>™</sup> 4 MCU kits, or connect PSOC<sup>™</sup> 4 MCU to a debugger such as CY8CKIT-002 PSOC<sup>™</sup> MiniProg3 Program and Debug Kit or CY8CKIT-005-A MiniProg4 Program and Debug Kit via a 10-pin or 5-pin connector (see Figure 8 for pin map). For a 10-pin connector, Samtec FTSH-105-01-L-DV-K (surface mount) or FTSH-105-01-L-D-K (through hole) is recommended. For a 5-pin connector, Molex 22-23-2051 is recommended. Similar parts are available from other vendors.

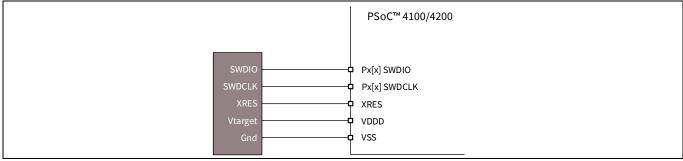

Figure 9 shows the SWD connections.

Figure 9 SWD connections to PSOC<sup>™</sup> 4100/PSOC<sup>™</sup> 4200

SWD pins are located in different ports in different device families. The pins could be used for other functionality, when the devices are not being programmed; see the device datasheet for the possible functionality details.

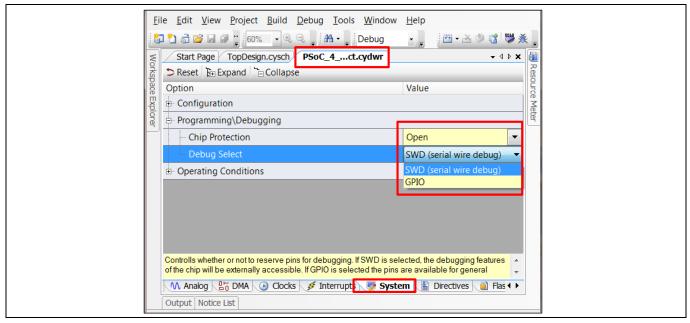

However, if you need to use SWD pins for run-time debugging, in PSOC<sup>™</sup> Creator select **SWD (serial wire debug)**, instead of **GPIO**, from the **Debug Select** pull-down list in the **System** tab of the DWR window as Figure 10 shows. To select the debug port in ModusToolbox<sup>™</sup> software, open the device configurator as shown in Figure 11. In this case, the pins cannot be used for other functionality any longer.

### Programming and debugging

| CY8C4149AZI       | -S598  |                                  |                 |                   |                                |       | Debug - Parameters           | 6 ×                                                |

|-------------------|--------|----------------------------------|-----------------|-------------------|--------------------------------|-------|------------------------------|----------------------------------------------------|

| Peripherals       | Pins   | Analog-Routing                   | System          | Peripheral-Clocks | DMA                            |       | Enter filter text            | Z U 🖻 🖽                                            |

| Enter filter text | t      |                                  |                 | 7 🗉 🗉 🖌 🗎         | r (                            | S. 52 | Name                         | Value                                              |

| Resource          |        | Name(s)                          |                 |                   |                                |       | ✓ General                    |                                                    |

| 🗹 Debug           |        | cpuss_0_dap_0                    |                 |                   |                                |       | ⑦ Debug Mode                 | SWD ~                                              |

| EM_EEP            | ROM    | srss_0_eeprom_0                  | -               |                   |                                |       | <ul> <li>SWD Pins</li> </ul> |                                                    |

| ✓ Power           |        |                                  |                 |                   |                                |       | SWDIO                        |                                                    |

|                   | Claska | srss_0_power_0<br>srss_0_clock_0 | IMO<br>48 MHz ± |                   |                                |       | (?) SWCLK                    | P3[3] digital_in (CYBSP_SWDCK) [USED]              |

|                   |        |                                  |                 |                   | Wetchdog Time<br>Wetchdog Cour |       |                              | Parameters to configure the<br>Debug mode settings |

| <                 |        |                                  | > <             |                   |                                | >     | Debug - Parameters           | Code Preview                                       |

Figure 11 ModusToolbox<sup>™</sup> software debugging settings in the device configurator

Note: In ModusToolbox<sup>™</sup> software, if you need to use SWD pins for other purposes, deselect the debug resource in the **System** tab of the device configurator and configure the pin name and state as required from **Pins** tab.

## 7 GPIO pins

PSOC<sup>™</sup> 4 MCU provides flexible GPIO pins. Each pin has 4 mA source or 8 mA sink capability. All GPIO pins can be controlled by firmware. Most of them also have alternative connections to PSOC<sup>™</sup> 4 MCU peripherals. Different components have different dedicated or fixed pins for their terminals. With dedicated pins, you get the best performance when the peripheral is connected to its own dedicated pin or pins. However, for flexibility, you can connect the peripheral to other pins at the cost of using some internal routing resources.

If a peripheral has fixed pins, then you can connect it to only those pins.

## 7.1 I/O pin selection

When you design a hardware system based on PSOC<sup>™</sup> 4 MCU, you should assign the GPIO pins in the following sequence. Note that pins with names in bold may be located at different pins of different ports for different PSOC<sup>™</sup> 4 MCU device families; check datasheets for details.

- 1. System function pins

- a) SWD: If you need run-time debugging, use the **SWD\_CLK** and **SWD\_DATA** pins.

- b) External clock: If you need to use an external clock, use the **EXT\_CLK** pin.

- c) External 32.768-kHz crystals: for applicable families, if you need a high-accuracy, low-frequency clock, use the **WCO\_IN** (or **XTAL32I**) pin and the **WCO\_OUT** (or **XTAL32O**) pin.

- d) Wakeup: This pin is used to wake up PSOC<sup>™</sup> 4 MCU from the Stop low-power mode. If you need this feature, use the **WAKEUP** pin. For more information, see AN86233 PSOC<sup>™</sup> 4 MCU low-power modes and power reduction techniques [3].

- 2. Analog pins

- a) SAR ADC: **SARMUX [7:0]** pins are used as multichannel inputs to the SAR ADC. In addition, if you want an ADC clock faster than 3 MHz or you need to apply an external reference, reserve VREF for an external bypass capacitor connection. See SAR ADC acquisition time for details.

**SARMUX [7:0]** pins are dedicated pins for the SAR ADC. Through the internal analog bus, you can also route signals from the other pins connected to the internal analog bus (See the device datasheet for this information) to the ADC. VREF is a fixed pin for the ADC's reference bypass capacitor connection.

- b) Low-power comparator: PSOC<sup>™</sup> 4 MCU has up to two comparators that can work in the Hibernate lowpower mode. Each comparator has two fixed pins, **COMPx\_INP** (or **LPCOMP.IN\_P[x]**) for noninverting input and **COMPx\_INN** (or **LPCOMP.IN\_P[x]**) for inverting input. Note that PSOC<sup>™</sup> 4100S, PSOC<sup>™</sup> 4100S Plus, PSOC<sup>™</sup> 4100S Plus 256K, PSOC<sup>™</sup> 4100 BL, PSOC<sup>™</sup> 4100S Max, PSOC<sup>™</sup> 4200DS, PSOC<sup>™</sup> 4100PS and PSOC<sup>™</sup> 4000T do not have the Hibernate low-power mode.

- c) Continuous Time Block mini (CTBm): PSOC<sup>™</sup> 4 MCU has up to two CTBm modules, each of which is composed of two opamps. One opamp has a dedicated noninverting input pin (**CTBx.OAx.INP**), a fixed inverting input pin (**CTBx.OAx.INN**), and a fixed output pin (**CTBx.OAx.OUT**). If you use an opamp as a comparator, you can route the digital output to a GPIO pin in Port 0, Port 1, Port 2, or Port 3.

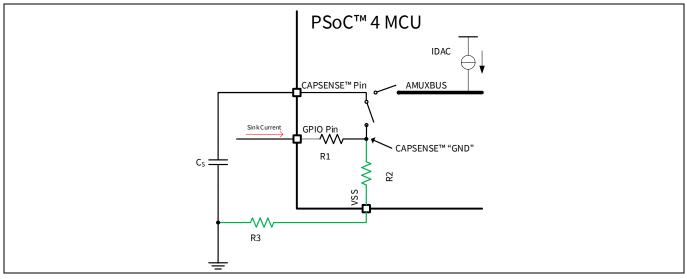

- d) CAPSENSE<sup>™</sup>: When you use this module, note that there are two fixed pins. You must connect a reservoir capacitor (C<sub>MOD</sub>) to **CMOD** (or **C\_MOD**) pin in all cases, and the other reservoir capacitor (C<sub>SH\_TANK</sub>) to **CTANK** (or **C\_SH\_TANK**) or **CMOD2** pin in some cases. Refer to the relevant device datasheet for information on pin number and capacitor value. You can connect any other pin to a CAPSENSE<sup>™</sup> sensor or shield. See AN85951 PSOC<sup>™</sup> 4 and PSOC<sup>™</sup> 6 MCU CAPSENSE<sup>™</sup> design guide [5] for details.

- e) Continuous Time Block (CTB): PSOC<sup>™</sup> 4100PS has up to two CTB modules, each of which is composed of two opamps and the associated resistor matrix. One opamp has a dedicated noninverting input pin (**CTBx.OAx.INP**), a fixed inverting input pin (**CTBx.OAx.INN**), and a fixed output pin (**CTBx.OAx.OUT**).

- f) Voltage DAC (VDAC): PSOC<sup>™</sup> 4100PS has a 13-bit VDAC module that can take input from port pins. The output of VDAC needs to be routed to a port pin through the CTB opamp.

- 3. Digital pins

- a) Timer/Counter Pulse-Width Modulator (TCPWM): PSOC<sup>™</sup> 4 MCU has up to eight TCPWM blocks. Each TCPWM can output two complementary PWM signals. All these signals are routed to dedicated GPIO pins via high-speed paths. See the device datasheet to learn more about these dedicated pins.

- b) You can also route these signals via an internal digital connection to other GPIO pins that support digital signal interconnect (DSI). See the respective device datasheet for more details.

- c) Serial Communication Block (SCB): PSOC<sup>™</sup> 4 MCU has up to four SCBs. Each SCB can be configured as SPI, I<sup>2</sup>C, or UART. Each SCB has fixed pins for its terminals. See the device datasheet to learn more about these pins. Note that PSOC<sup>™</sup> 4100PS has up to three SCBs.

- d) PSOC<sup>™</sup> 4000 and PSOC<sup>™</sup> 4000T can multiplex the SWD and I2C pins on a pair of dedicated GPIO pins, it is useful if running short of GPIOs.

- e) Controller Area Network (CAN): PSOC<sup>™</sup> 4 MCU has up to two CANs. These have fixed pins for its terminals.

- f) Universal Serial Bus (USB): PSOC<sup>™</sup> 4 MCU has fixed pins for USB connectivity. See the respective device datasheet for more details.

Unlike TCPWM, the SCB terminals are routed to fixed pins and cannot be routed to any other GPIO pin. You must follow the fixed pin assignments when using the SCBs.

If your system needs a serial communication interface with a more flexible GPIO pin assignment, you can use a Universal Digital Block (UDB) to implement it in the applicable devices. See the PSOC<sup>™</sup> 4 architecture reference manual for details.

## 7.2 Special ports

In PSOC<sup>™</sup> 4 MCU, certain groups of ports have interconnect fabric different from the fabric the other ports have. Therefore, some of the flexible configurations are not available on them. Use the following table as a guideline in the system design. "Y" means the port(s) support the functionality; "N" means the port(s) do not.

|                                              | PSO<br>4000   |   | PSOC™<br>4000T   | PSOC™<br>4000S/<br>4100S | PSOC™<br>4100PS     | PSOC™<br>4500S            | PSO<br>4100<br>4200 | 1 | PSOC™<br>4100M/<br>4200M |               | PSO0<br>4100<br>4200 | BLE/    | PSOC™<br>4100L/<br>4200L             | 1                           | PSOC<br>™<br>4100S<br>Plus      | PSOC™<br>4100S<br>Max                                |

|----------------------------------------------|---------------|---|------------------|--------------------------|---------------------|---------------------------|---------------------|---|--------------------------|---------------|----------------------|---------|--------------------------------------|-----------------------------|---------------------------------|------------------------------------------------------|

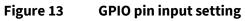

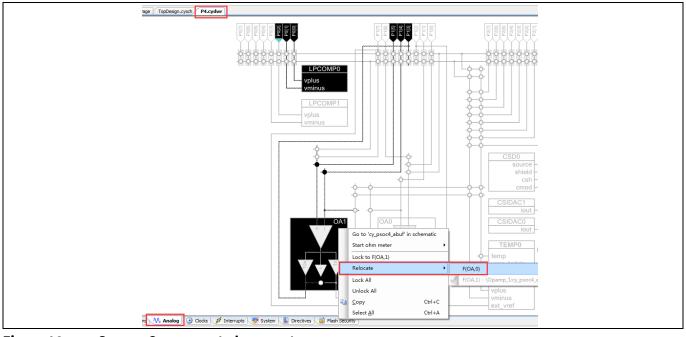

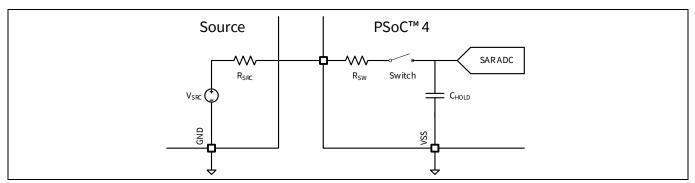

| Port number                                  | 0,<br>1,<br>2 | 3 | 0, 1, 2,<br>3, 4 | 0, 1, 2,<br>3, 4         | 0, 1, 2,<br>3, 4, 5 | 0, 1, 2, 3,<br>4, 5, 6, 7 | 0,<br>1,<br>2,<br>3 | 4 | 0, 1,<br>2, 3            | 4, 5,<br>6, 7 | 0,<br>1,<br>2,<br>3  | 4,<br>5 | 0, 1,<br>2, 3,<br>4, 5,<br>10,<br>11 | 6, 7,<br>8, 9,<br>12,<br>13 | 0, 1,<br>2, 3,<br>4, 5,<br>6, 7 | 0, 1, 2,<br>3, 4, 5,<br>6, 7, 8,<br>9, 10,<br>11, 12 |